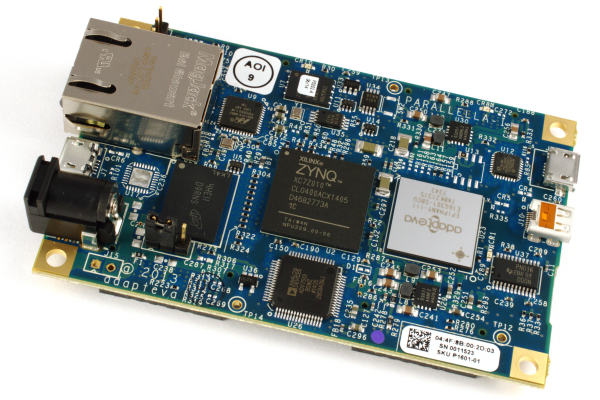

A few weeks ago I gave a talk to a group of graduate students at Chalmers University of Technology in Gothenburg Sweden. The talk was part of a 12 week course (Chalmers Computing Labs Tech Talks) intended to bridge the world of academia and industry by inviting speakers to talk about difficult product problems (and solutions) from different industries. Professor Mary Sheeran, who invited me, wanted to hear more about the design process used to design the Epiphany parallel processor and the Parallella $99 single board computer.

Preparing the slides and doing a post-mortem on 7 years of parallel processor design was a fun (but exhausting…) trip down memory lane and the interaction with the (~30) students was fantastic!

The writing is terse but some of the (painful) lessons learned may be useful to folks working in the field of computer architecture and hardware development.

If anything is unclear or you want to discuss content just leave a comment…

Cheers,

Andreas