OpenSHMEM 1.4 for Epiphany is available now as open source software on GitHub [0]. Compared to the previous announcement [1], OpenSHMEM 1.4 provides new functionality for Epiphany including, but not limited to: Adding shmem_sync_all and shmem_sync to provide PE synchronization without completing pending communication operations Adding shmem_test function, which tests whether a variable on the local PE has changed Adding shmem_calloc…

The latest version of ePython makes it possible to take existing Python code and offload specific functions (we tend to call them kernels) to the Epiphany cores. This is really viewing the Epiphany as an accelerator, where codes run on the host (the Parallella) and specific computationally intensive kernels are then offloaded to the accelerator for execution. The good news…

For an update regarding Adapteva and how it relates to Parallella, please see Andreas’ latest blog post.

The Epiphany coprocessor has 16 CPU cores, but they are configured differently than the 16 cores you might find in an Intel Xeon processor. The Xeon processor is configured as a Symmetric Multiprocessor (SMP) [0] where all cores have shared access to a single main memory. Programming models like OpenMP and OpenCL are more suitable for SMP architectures. In contrast,…

A newly developed compiler [0] and paper describing the parallel language [1] are released today which enable a novel approach to parallel and distributed programming for the many-core Epiphany coprocessor included in Parallella as well as multi-core CPUs and distributed clusters. The LOLCODE language, originally developed in 2007, has been extended to include parallel and distributed programming concepts directly within…

At the recent HiPEAC conference in Stockholm, Andreas Olofsson presented lessons learned from nine years at Adapteva. Slides (PDF) —- Andreas Olofsson, “What I learned building a microprocessor chip company from scratch”, EnESCE: 2017 Workshop on Energy-efficient Servers for Cloud and Edge Computing

At the recent HiPEAC conference in Stockholm, Andreas Olofsson presented a path to the world’s first million core RISC microprocessor. Slides (PDF) —- Andreas Olofsson, “How to build a million core processor”, MULTIPROG: 2017 International Workshop on Programmability and Architectures for Heterogeneous Multicores

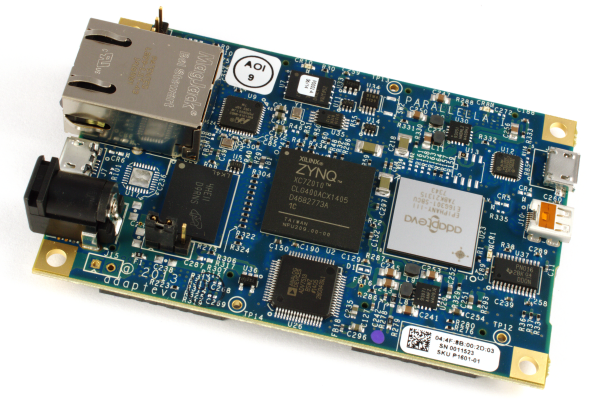

When we set out to design the credit card sized Parallella board in 2012, we knew it was going to run hot. Five Watts is just too much power to suck out of a credit card with active cooling! We thought Parallella developers would have fun creating their own cooling solutions, but that turned out to be a poor assumption.. Finally last…

A couple of years ago, Ola Jeppsson started working on a 1024-core simulator as part of his Master’s Thesis at Chalmer’s University in Sweden. (advisor, Sally McKee). He picked up the project again in 2016 as part of the validation process of the 1024-core Epiphany-V. Debugging with the simulator is an order of magnitude easier than with hardware, so you should…

Thanks to a multi-year collaboration with the development tools group at Ericsson, Parallella is now leading the charge in FREE (as in FREEDOM and BEER) parallel debugging! An initial prototype of the debugger and visualizer was created in 2013, which was presented at EclipseCon, but we were never able to get it to a releasable state. Now thanks to a…